Synchronous Counter Design

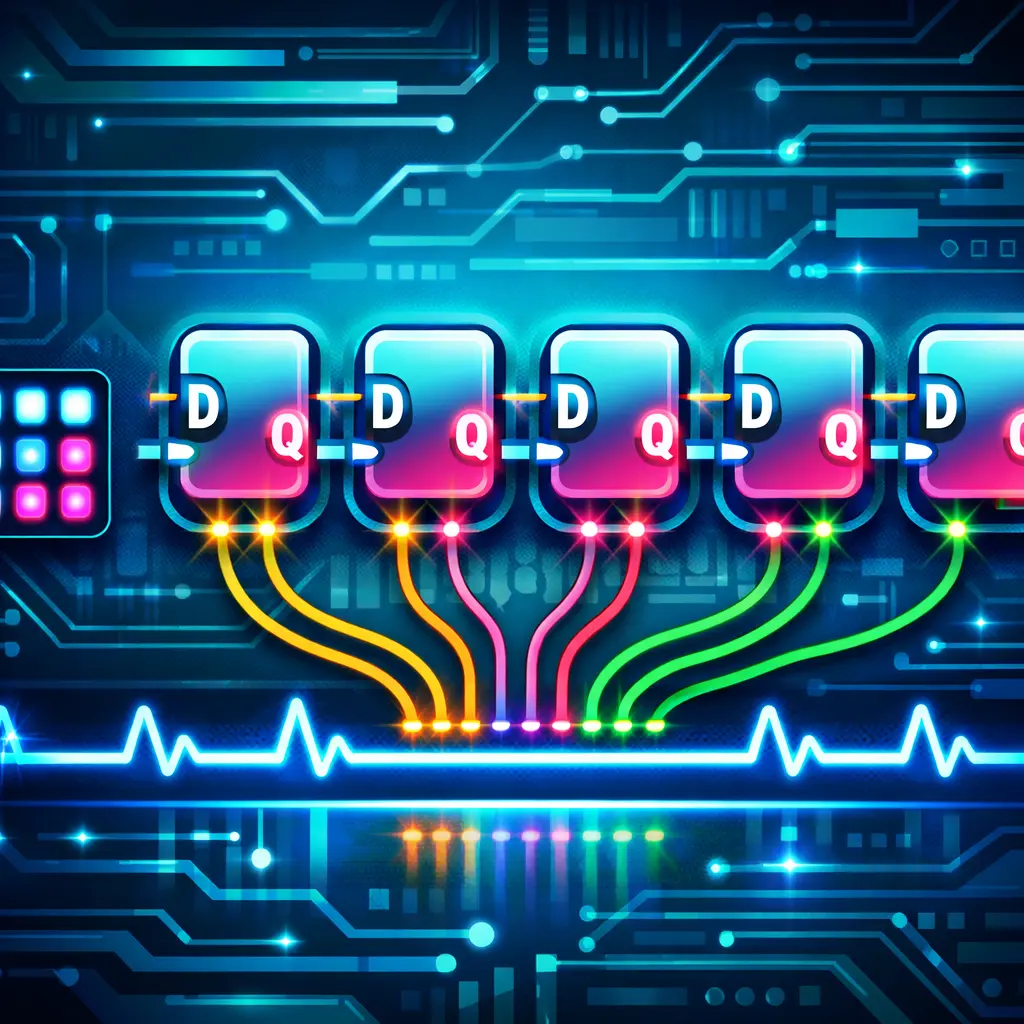

Synchronous counter design refers to creating digital circuits where all flip-flops are triggered simultaneously by a common clock signal. This ensures that state changes occur in unison, minimizing timing errors and glitches. Synchronous counters are widely used in digital electronics and computing for counting, sequencing, and timekeeping tasks. Their predictable behavior and faster operation, compared to asynchronous counters, make them essential in applications requiring precise and reliable counting operations.

Synchronous Counter Design

Synchronous counter design refers to creating digital circuits where all flip-flops are triggered simultaneously by a common clock signal. This ensures that state changes occur in unison, minimizing timing errors and glitches. Synchronous counters are widely used in digital electronics and computing for counting, sequencing, and timekeeping tasks. Their predictable behavior and faster operation, compared to asynchronous counters, make them essential in applications requiring precise and reliable counting operations.

💡 Key Takeaways

- Distinguish synchronous vs asynchronous counters and benefits of a single clock.

- Build a binary counter with flip-flops and next-state logic driven by a common clock.

- Extend to modulo-N and up/down counters using terminal-count detection and load/reset logic.

- Address practical design considerations: synchronous reset/enable, propagation delays, and glitch avoidance.

❓ Frequently Asked Questions

What is a synchronous counter?

A digital counter where all flip-flops share a common clock edge, so all bits update together.

How does a synchronous counter differ from an asynchronous (ripple) counter?

In a ripple counter, each flip-flop toggles based on the previous stage, causing propagation delays. In a synchronous counter, all stages are clocked simultaneously with combinational logic determining when each bit toggles, offering consistent timing.

What components are typically used in synchronous counter design?

JK or T flip-flops with a common clock, plus combinational logic (AND/OR gates) to generate the proper toggle signals for higher bits. D flip-flops can also be used with appropriate next-state equations.

How do you implement a simple 4-bit synchronous binary counter?

Clock four flip-flops (Q0–Q3) with the same clock. For JK version: J0=K0=1; J1=K1=Q0; J2=K2=Q0 AND Q1; J3=K3=Q0 AND Q1 AND Q2. Add a synchronous clear for reset if needed; the counter counts 0 to 15 and wraps to 0.